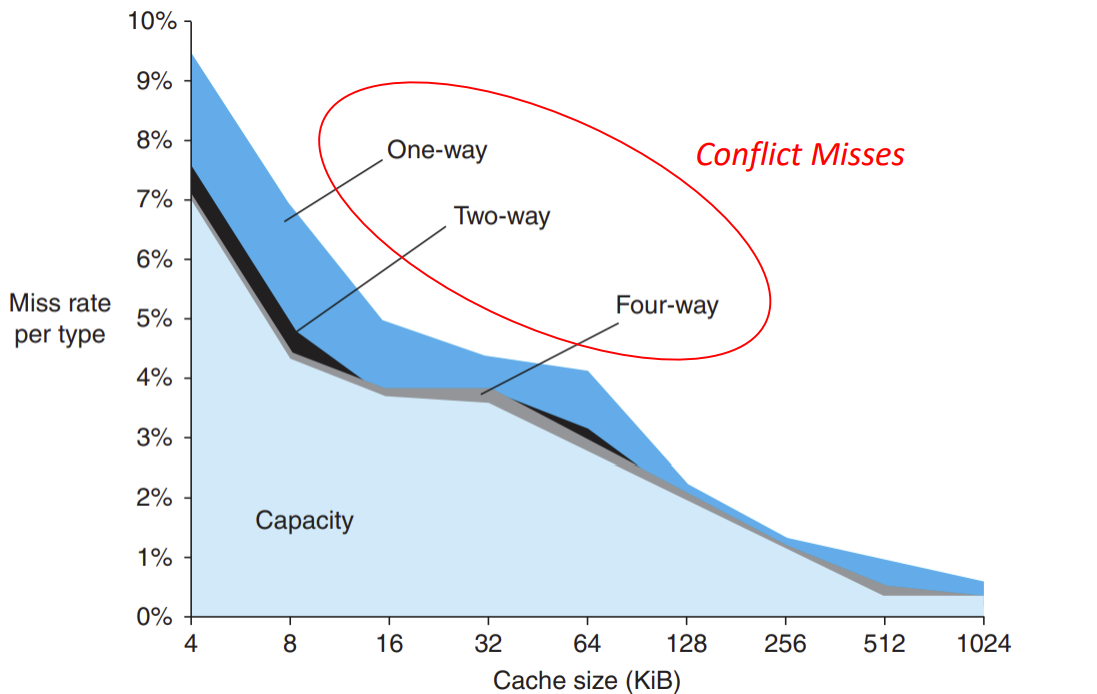

경희대학교 김정욱 교수님의 컴퓨터 구조 수업을 기반으로 정리한 글입니다.Common Framework for Memory Hierarchy▶ cache / main memory TLB는 address를 mapping하는 정보밖에 없기 때문에, data를 포함한 캐시보다 작다. 용량이 클수록 miss rate가 낮다. 때문에 miss rate은 L1 > L2 > main memory ※ 용량 - L1: layer 1 cache Block Placement of Memory HierarchyQ1. Block이 어디에 위치할 수 있는가?▶ Direct mapped / Set associative / Fully associative ▶ Miss rate 확률 cache size가 증가할수록 miss rate 감..